Predstavitev čipa gonilnika LED

s hitrim razvojem industrije avtomobilske elektronike se gonilniški čipi LED visoke gostote s širokim razponom vhodne napetosti pogosto uporabljajo v avtomobilski razsvetljavi, vključno z zunanjo sprednjo in zadnjo osvetlitvijo, notranjo osvetlitvijo in osvetlitvijo zaslona.

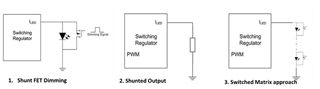

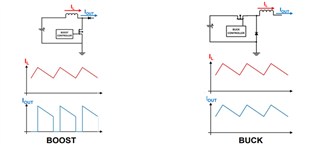

Gonilne čipe LED lahko razdelimo na analogno zatemnitev in zatemnitev PWM glede na metodo zatemnitve.Analogno zatemnitev je razmeroma preprosto, zatemnitev PWM je razmeroma zapletena, vendar je obseg linearne zatemnitve večji od analogne zatemnitve.LED gonilniški čip kot razred čipov za upravljanje porabe energije, njegova topologija predvsem Buck in Boost.izhodni tok vezja je neprekinjen, tako da je valovanje izhodnega toka manjše, kar zahteva manjšo izhodno kapacitivnost, kar je bolj ugodno za doseganje visoke gostote moči vezja.

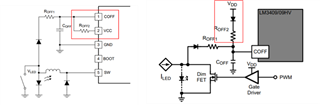

Slika 1 Povečanje izhodnega toka proti Bucku

Slika 1 Povečanje izhodnega toka proti Bucku

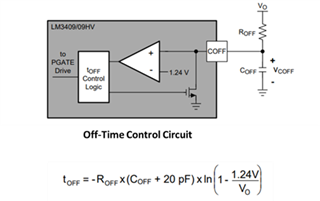

Pogosti načini krmiljenja gonilnih čipov LED so trenutni način (CM), način COFT (nadzorovan čas izklopa), način COFT & PCM (način največjega toka).V primerjavi s krmiljenjem trenutnega načina krmilni način COFT ne zahteva kompenzacije zanke, kar vodi k izboljšanju gostote moči, hkrati pa ima hitrejši dinamični odziv.

Za razliko od drugih načinov krmiljenja ima čip načina krmiljenja COFT ločen zatič COFF za nastavitev časa izklopa.Ta članek predstavlja konfiguracijo in previdnostne ukrepe za zunanje vezje COFF, ki temelji na tipičnem gonilnem čipu Buck LED, ki ga krmili COFT.

Osnovna konfiguracija COFF in previdnostni ukrepi

Načelo krmiljenja načina COFT je, da ko induktorski tok doseže raven izklopnega toka, se zgornja cev izklopi in spodnja cev vklopi.Ko čas izklopa doseže tOFF, se zgornja cev ponovno vklopi.Ko se zgornja cev izklopi, ostane izklopljena konstanten čas (tOFF).tOFF nastavita kondenzator (COFF) in izhodna napetost (Vo) na obrobju vezja.To je prikazano na sliki 2. Ker je ILED strogo reguliran, bo Vo ostal skoraj konstanten v širokem razponu vhodnih napetosti in temperatur, kar ima za posledico skoraj konstanten tOFF, ki ga je mogoče izračunati z uporabo Vo.

Slika 2. Krmilno vezje časa izklopa in formula za izračun tOFF

Slika 2. Krmilno vezje časa izklopa in formula za izračun tOFF

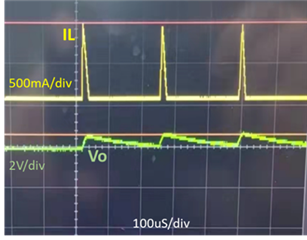

Upoštevati je treba, da ko izbrani način zatemnitve ali zatemnitveno vezje zahteva kratkostični izhod, se vezje trenutno ne bo pravilno zagnalo.V tem času postane valovanje toka induktorja veliko, izhodna napetost postane zelo nizka, veliko nižja od nastavljene napetosti.Ko pride do te okvare, bo tok induktorja deloval z največjim časom izklopa.Običajno najdaljši čas izklopa, nastavljen znotraj čipa, doseže 200us~300us.V tem času se zdi, da tok induktorja in izhodna napetost preideta v način kolcanja in ne moreta normalno izhajati.Slika 3 prikazuje nenormalno valovno obliko induktorskega toka in izhodne napetosti TPS92515-Q1, ko se za obremenitev uporablja ranžirni upor.

Slika 4 prikazuje tri vrste tokokrogov, ki lahko povzročijo zgornje napake.Ko se za zatemnitev uporablja shunt FET, je za obremenitev izbran shunt upor, obremenitev pa je preklopno matrično vezje LED, vsi lahko povzročijo kratek stik v izhodni napetosti in preprečijo normalen zagon.

Slika 3 Tok in izhodna napetost induktorja TPS92515-Q1 (kratka napaka izhodne obremenitve upora)

Slika 3 Tok in izhodna napetost induktorja TPS92515-Q1 (kratka napaka izhodne obremenitve upora)

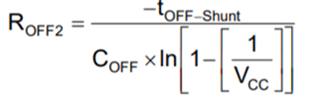

Slika 4. Tokokrogi, ki lahko povzročijo kratke stike na izhodu

Da bi se temu izognili, je za polnjenje COFF še vedno potrebna dodatna napetost, tudi ko je izhod v kratkem stiku.Vzporedno napajanje, za katerega je mogoče uporabiti VCC/VDD, polni kondenzatorje COFF, vzdržuje stabilen čas izklopa in ohranja konstantno valovanje.Stranke lahko pri načrtovanju vezja rezervirajo upor ROFF2 med VCC/VDD in COFF, kot je prikazano na sliki 5, da olajšajo kasnejše odpravljanje napak.Hkrati podatkovni list čipa TI običajno poda posebno formulo za izračun ROFF2 glede na notranje vezje čipa, da stranki olajša izbiro upora.

Slika 5. Zunanje izboljšano vezje SHUNT FET ROFF2

Slika 5. Zunanje izboljšano vezje SHUNT FET ROFF2

Če za primer vzamemo izhodno napako kratkega stika TPS92515-Q1 na sliki 3, se spremenjena metoda na sliki 5 uporabi za dodajanje ROFF2 med VCC in COFF za polnjenje COFF.

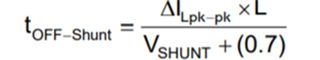

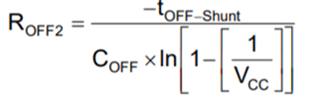

Izbira ROFF2 je postopek v dveh korakih.Prvi korak je izračun zahtevanega časa izklopa (tOFF-Shunt), ko je za izhod uporabljen shunt upor, kjer je VSHUNT izhodna napetost, ko se za obremenitev uporablja shunt upor.

Drugi korak je uporaba tOFF-Shunt za izračun ROFF2, ki je naboj od VCC do COFF prek ROFF2, izračunan na naslednji način.

Drugi korak je uporaba tOFF-Shunt za izračun ROFF2, ki je naboj od VCC do COFF prek ROFF2, izračunan na naslednji način.

Na podlagi izračuna izberite ustrezno vrednost ROFF2 (50k Ohm) in povežite ROFF2 med VCC in COFF v primeru napake na sliki 3, ko je izhod vezja normalen.Upoštevajte tudi, da mora biti ROFF2 veliko večji od ROFF1;če je prenizek, bo TPS92515-Q1 imel težave z minimalnim časom vklopa, kar bo povzročilo povečan tok in možno poškodbo naprave na čipu.

Na podlagi izračuna izberite ustrezno vrednost ROFF2 (50k Ohm) in povežite ROFF2 med VCC in COFF v primeru napake na sliki 3, ko je izhod vezja normalen.Upoštevajte tudi, da mora biti ROFF2 veliko večji od ROFF1;če je prenizek, bo TPS92515-Q1 imel težave z minimalnim časom vklopa, kar bo povzročilo povečan tok in možno poškodbo naprave na čipu.

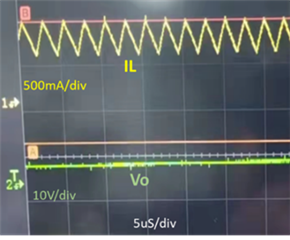

Slika 6. Tok in izhodna napetost tuljave TPS92515-Q1 (normalno po dodajanju ROFF2)

Slika 6. Tok in izhodna napetost tuljave TPS92515-Q1 (normalno po dodajanju ROFF2)

Čas objave: 15. februarja 2022